# S1985 MSX-SYSTEMII APPLICATION MANUAL

----- YAMAHA CORPORATION -----

Scanned, ocr'ed and converted to PDF by HansO, 2001

## TABLE OF CONTENTS

| 1. | MSX-SYSTEM II                                                   |    |

|----|-----------------------------------------------------------------|----|

|    | Overview                                                        | 1  |

|    | Features                                                        | 1  |

| 2. | Functional overview                                             |    |

|    | Pin layout                                                      |    |

|    | Pin functions                                                   |    |

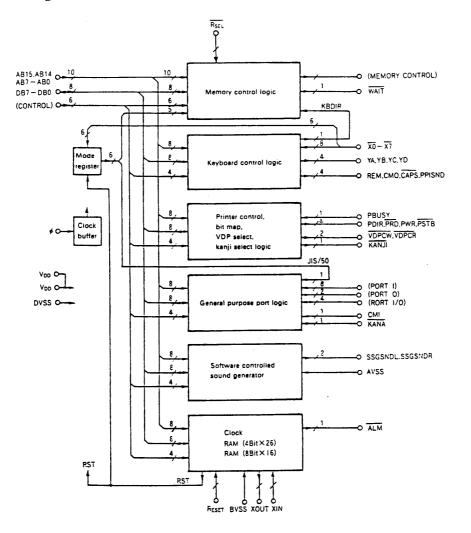

|    | Block diagram                                                   | 5  |

| 3. | Description of functions                                        |    |

|    | Selection of functions                                          |    |

|    | Back-up and reset                                               | 7  |

|    | Expansion slot register                                         | 8  |

|    | Address map and slot expansion                                  | 9  |

|    | I/O addresses and functions                                     | 10 |

|    | Bit allocations of keyboard and slot designation registers      |    |

|    | Back-up RAM (8 bit X 16)                                        | 12 |

|    | Bit map function                                                | 12 |

|    | Printer                                                         |    |

|    | Kanji ROM select signal and system control                      | 15 |

|    | Mapper                                                          | 15 |

|    | Keyboard bus direction                                          | 16 |

| 4. | SSG and general purpose ports                                   |    |

|    | Register array                                                  | 17 |

|    | General purpose ports                                           | 18 |

|    | Setting of music frequencies                                    | 18 |

|    | Setting of noise generator                                      | 19 |

|    | Settings of mixer                                               | 19 |

|    | Level control                                                   |    |

|    | Setting of envelope frequency                                   | 20 |

|    | Envelope shape control                                          | 21 |

|    | D-A Convertor                                                   | 22 |

|    | Sound output SSGSNDL and SSGSNDR                                | 23 |

| 5. |                                                                 |    |

|    | Address allocations and initial state of counters and registers | 24 |

|    | Allocation of addresses and functions                           | 24 |

|     | Mode setting and alarm/timer EN function                   | 25 |

|-----|------------------------------------------------------------|----|

|     | Reset control function and 16Hz/1Hz register setting       | 25 |

|     | Test registers                                             | 25 |

|     | Setting of 12/24 selector                                  |    |

|     | Setting of leap year                                       |    |

|     | Setting and reading the time and calender                  |    |

|     | Alarm setting and reading                                  |    |

|     | RAM (4 bit X 26)                                           |    |

|     |                                                            |    |

| 6.  | Oscillation circuit                                        | 27 |

| ••• |                                                            |    |

| 7.  | Voltage characteristics of clock oscillation circuit       | 28 |

|     | Temperature characteristics of clock oscillation circuit   | 29 |

|     | •                                                          | ι. |

| 8.  | Back-up voltage and current                                | 30 |

|     |                                                            | ,  |

| 9.  | Electrical characteristics                                 | 31 |

|     |                                                            |    |

| 10. | Recommended operating conditions                           | 31 |

|     |                                                            |    |

| 11. | DC characteristics                                         | 31 |

|     |                                                            |    |

| 12. | AC characteristics                                         |    |

|     | Clock timing                                               |    |

|     | Write timing                                               |    |

|     | Read timing                                                |    |

|     | Reset timing                                               | 33 |

|     | Analog output                                              | 33 |

|     | Timing of M1 cycle, Memory read/write cycle, and I/O cycle | 34 |

|     |                                                            |    |

| 13. | Precautions for use                                        | 40 |

|     |                                                            |    |

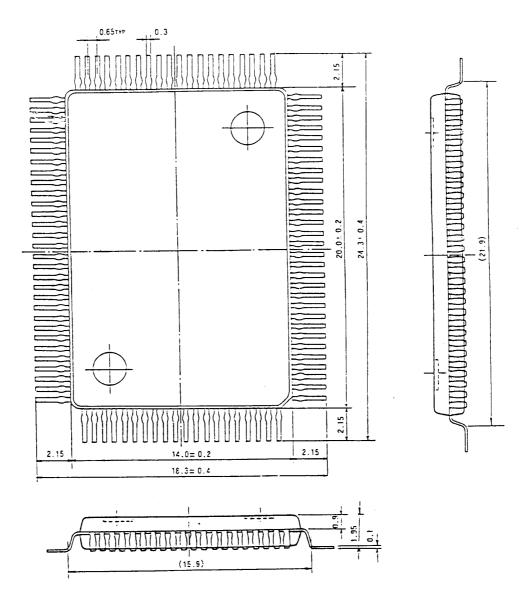

| 14. | External view                                              | 41 |

## 1. MSX-SYSTEM II

#### Overview

The Yamaha S1985 is an LSI device designed for use with MSX2 computers. It is capable of memory control with expansion according to MSX2 specifications taken into account, and control of peripheral equipment such as a VDP, keyboard, printer, etc. It also has a built-in SSG for generation of music signals and a clock.

#### Features

Slot control can be expanded to slots 0 and 3 Mapper function allowing memory expansion up to 512K bytes Built-in MSX2 standard clock functions 16 byte (8 bit) back-up RAM Registers for foreground and background color reading as bit mapped functions DRAM refresh can be selected as RAS only refresh and hidden refresh VDP select signal output Keyboard access Two built-in joystick port Built-in SSG (Yamaha YM2149 equivalent) : 8 octaves Voicing range : 3 sine waves voicing systems and 1 noise voicing system Voicing systems : 5 bit Envelope control D-A convertor : 5 bit Bi-directional printer mode CMOS device with Si gates 100 pin flat plastic package

## 2. Functional Overview

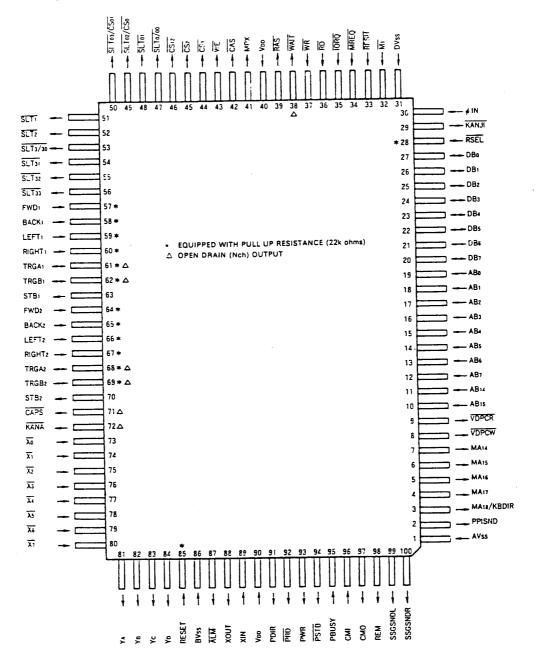

Pin layout

## Pin functions

| Pin name                           | I/O | Function                                                |

|------------------------------------|-----|---------------------------------------------------------|

| AB15, AB14, AB7~AB0                | i   | Address bus input (10 bits) for Z80A CPU                |

| DB7~DB0                            | i/o | Data bus input/output (8 bits) for Z80A CPU             |

| MI                                 | i   | M1 input for Z80A CPU                                   |

| RFSH                               | i   | RFSH input for Z80A CPU                                 |

| MREQ                               | i   | MREQ input for Z80A CPU                                 |

| IORQ                               | i   | IORQ input for Z80A CPU                                 |

| RD                                 | i   | RD input for Z80A CPU                                   |

| WR                                 | i   | WR input for Z80A CPU                                   |

| WAIT                               | 0   | WAIT signal output to Z80A CPU (can have wired logic)   |

| MPX                                | 0   | Multiplex signal output for DRAM address                |

| RAS                                | 0   | DRAMS RAS signal output                                 |

| CAS                                | ο   | DRAMS CAS signal output                                 |

| WE                                 | ο   | DRAM WE signal output                                   |

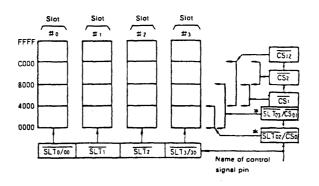

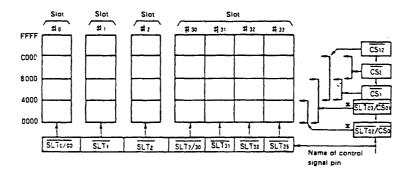

| SLT33                              | 0   | Slot # 33 select signal output                          |

| SLT32                              | 0   | Slot # 32 select signal output                          |

| SLT31                              | 0   | Slot # 31 select signal output                          |

| SLT3/30                            | ο   | Slot # 3 or 30 select signal output                     |

| SLT2                               | 0   | Slot # 2 select signal output                           |

| SLT1                               | 0   | Slot # 1 select signal output                           |

| SLT03/CS01                         | 0   | Slot #03 select or ROM select 0000H~7FFFH signal output |

| SLT02/CS0                          | o   | Slot #02 select or ROM select 0000H~3FFFH signal output |

| SLT01                              | . 0 | Slot # 01 select signal output                          |

| SLT0/00                            | 0   | Slot # 0 or 00 select signal output                     |

| CS2                                | 0   | ROM select 8000H~BFFFH signal output                    |

| CS1                                | 0   | ROM select 4000H~7FFFH signal output                    |

| CS12                               | 0   | ROM select 4000H~BFFFH signal output                    |

| MA18/KBDIR                         | 0   | Mapper address or keyboard bus direction signal output  |

| MA17~14                            | o   | Mapper address address signal output                    |

| YD~YA                              | 0   | Keyboard drive signal input                             |

| $\overline{X7} \sim \overline{X0}$ | i   | Keyboard return signal input                            |

| CAPS                               | 0   | Caps LED signal output                                  |

| KANA                               | 0   | Kana LED signal output                                  |

| CMI                                | i   | Cassette read signal input                              |

| СМО                                | 0   | Cassette write signal output                            |

| REM                                | 0   | Cassette control signal output                          |

| PBUSY                              | i   | Printer busy signal input                               |

| PSTB                               | 0   | Printer strobe signal output                            |

| PWR                                | 0   | Printer write signal output                             |

| PRD                                | 0   | Printer read signal output                              |

| PDIR                               | 0   | Printer direction signal output                         |

| FWD1, FWD2                         | i   | Joystick FWD signal input (general purpose port input)  |

| BACK1, BACK2                       | i   | Joystick BACK signal input (general purpose port input) |

| ,                                  |     | 3                                                       |

|                                    |     |                                                         |

| LEFT1, LEFT2   | i   | Joystick LEFT signal input (general purpose port input)      |

|----------------|-----|--------------------------------------------------------------|

| RIGHT1, RIGHT2 | i   | Joystick RIGHT signal input (general purpose port input)     |

| TRGA1, TRGA2   | i/o | Joystick TRGA signal input/output (general purpose port      |

| , ,            |     | input/output)                                                |

| TRGB1, TRGB2   | i/o | Joystick TRGB signal input/output (general purpose port      |

|                |     | input/output)                                                |

| STB1, STB2     | о   | General purpose port output                                  |

| VDPSW          | 0   | VDP write signal output                                      |

| VDPCR          | 0   | VDP read signal output                                       |

| KANJI          | о   | Kanji ROM select signal output                               |

| RSEL           | i   | Signal input for expansion slot designation register control |

| RESET          | i   | Reset signal input                                           |

| PPISND         | 0   | PPI sound signal output                                      |

| SSGSNDL        | 0   | SSG sound LEFT signal output                                 |

| SSGSNDR        | 0   | SSG sound RIGHT signal output                                |

| Ø              | i   | Clock signal input                                           |

| VDD            |     | + 5V                                                         |

| DVSS           |     | 0 <sup>v</sup> (GND)                                         |

| AVSS           |     | GND for sound generation                                     |

| XIN            | i   | Input from clock crystal                                     |

| XOUT           | 0   | Output to clock crystal                                      |

| ALM            | 0   | Alarm signal output                                          |

| BVSS           |     | Power supply for clock back-up                               |

## Block diagram

(CONTROL) :MI, RFSH, MREQ, IORQ, RD, WR

(MEMORY CONTROL): RAS, MPX, CAS, WE, CSI, CS2, CS12, SLT0/00, SLT01, SLT02/CS0, SLT03/CS01, SLT1, SLT30/30, SLT2, SLT31, SLT32, SLT33, MA14, MA15, MA16, MA17, MA18/KBDIR

(PORTI) :FWD1, FWD2, BACK1, BACK2, LEFT1, LEFT2, RIGHT1, RIGHT2.

(PORTO) :STB1, STB2

(PORTI/O) :TRGA1, TRGA2, TRGB1, TRGB2

## 3. Description of functions

## Selection of functions

When the reset signal is input, the levels applied to the keyboard return input pins are latched by the internal reset signals to select the default functions.

#### Table of initial levels and functions

| Pin name       | Level | Function                                                                                                 |

|----------------|-------|----------------------------------------------------------------------------------------------------------|

|                | 0     | RAS only refresh mode selected                                                                           |

| <u>X2</u>      | 1     | Hidden refresh mode selected                                                                             |

|                | 0     | Mapper address output to MA18/KBDIR pin                                                                  |

| X5             | 1     | Keyboard bus direction output to MA18/KBDIR pin                                                          |

|                | 0     | Kana JIS layout                                                                                          |

| X6             | 1     | Kana syllabary layout                                                                                    |

|                | 0     | Single wait requested for VDP read or write                                                              |

| <del>X</del> 7 | 1     | Single wait not requested for VDP read or write                                                          |

|                | 0     | $\overline{SLT03}/\overline{CS01}$ and $\overline{SLT02}/\overline{CS0}$ pins output slot select signals |

| X3             | 1     | SLT03/CS01 and SLT02/CS0 pins output ROM select signals                                                  |

|                | 0     | Expansion to slot 0                                                                                      |

| XI ·           | 1     | No expansion to slot 0 when $\overline{X3} = 1$                                                          |

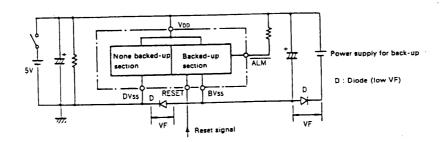

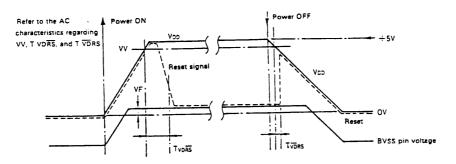

#### Back-up and reset

This devices uses the BVSS pin of the negative potential side to allow for back-up of the RAM data (4 bit  $\times$  26 and 8 bit  $\times$ 16).

Although a reset occurs when voltage of level "1" is applied to the RESET pin, the following precautions must be heeded to prevent loss of data and improper clock operation during switching between the back-up power supply and 5V power supply, and vice versa.

- When turning on the power supply with the device in the backed- up state, release the reset signal only after the level of the 5V power supply fully approaches 5V and all input levels to the device have stabilized.

- When switching off the power supply and shifting to the backed- up state, apply the reset signal and shift to back-up when the level of the 5V power supply starts to drop but is still close to 5V, and all input signals to the device are still stable.

There are various methods available for switching between the 5V power supply and back-up power supply. An example of a possible circuit and its operation are shown below.

As shown in this diagram, there are no problems as the forward direction electrical potential (VF) for the diodes is merely shifted so that voltage to the BVSS pin of the backed-up section is supplied from the 5V power supply when it is operating, or the back-up battery when it is not. However, when the alarm function is activated and output is fetched from the  $\overline{ALM}$  pin, this current will alter the VF value. This will cause the power supply voltage for the backed-up section to fluctuate according to the output from the  $\overline{ALM}$  pin. This problem can be solved by having the resistance of the load connected to the  $\overline{ALM}$  pin as high as possible, by using a circuit which limits fluctuations in the electrical potential corresponding to VF in relation to the current from the  $\overline{ALM}$  pin, or by not connecting load resistance to the  $\overline{ALM}$  pin when the alarm function is not used.

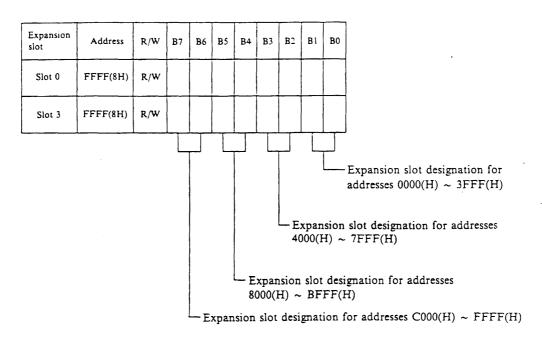

#### Expansion slot register

There are two registers for designation of the expansion slot: one for slot 0 and the other for slot 3. Expansion to both of the slots at the same time is possible. The inverse value of the contents is output when the registers are read. The address of the registers is FFFF(H) allowing slot expansion by input of the symbol obtained from NAND logic addresses AB8 ~ AB13 to the RSEL pin.

The slot expansion function is controlled by the level of the  $\overline{X1}$  and  $\overline{X3}$  pins when the device is reset. Refer to section on selection of this function.

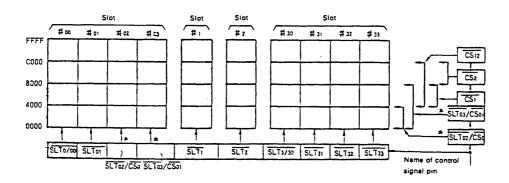

## Address map and slot expansion

No expansion

Expansion to slot 3

Expansion to slots 0 and 3

Note: The prescribed input is made to the RSEL pin for slot expansion. The function of the signals marked with asterisks is selected when the device is reset. They cannot be used at the same time when expansion is to slot 0.

| I/C | ) addresse | s and f | unctions |

|-----|------------|---------|----------|

|-----|------------|---------|----------|

| Function       | I/O address | W/R | Description                                       |

|----------------|-------------|-----|---------------------------------------------------|

| Back-up        | 40(H)       | W/R | Manufacturer ID number register                   |

| RAM            | 41          | w   | Back-up RAM address latch                         |

|                | 42          | W/R | Back-up RAM write/read                            |

| Bit map        | 46          | w   | Foreground/background color write                 |

|                | 47          | W/R | Pattern and foreground/background color read      |

| Printer        | 90          | W/R | Printer strobe write, printer status read         |

|                | 91          | W/R | Printer data write/read                           |

|                | 93          | w   | Printer bus direction                             |

| VDP            | 98~9F       | w   | VDP write                                         |

| _              | 98~9F       | R   | VDP read                                          |

| SSG            | AB0         | w   | SSG address latch                                 |

|                | AB1         | w   | SSG data write                                    |

|                | AB2         | R   | SSG data read                                     |

| Keyboard and   | A8          | W/R | slot designation                                  |

| Slot designa-  | A9          | R   | Keyboard return signal read                       |

| tion register  | AA          | W/R | Keyboard drive, cassette and PPI sound write/read |

|                | AB          | w   | Mode designation                                  |

| Clock and slot | B4          | w   | Clock and back-up RAM address latch               |

| designation    | B5          | W/R | Clock and back-up RAM write/read                  |

| Kanji          | D8, D9      | W/R | Kanji write/read                                  |

| System control | F5          | w   | System control                                    |

| Mapper         | FC          | W/R | Mapper register page 0                            |

|                | FD          | W/R | Mapper register page 1                            |

|                | FE          | W/R | Mapper register page 2                            |

|                | FF          | W/R | Mapper register page 3                            |

| Function                                 | Bit                                  | W/R |                                                          | Description                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |

|------------------------------------------|--------------------------------------|-----|----------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Slot designa-<br>tion register           | 0<br>1                               |     |                                                          | Slot designation signal for addresses $0000(H) \sim 3FFF(H)$                                                                                                                                                                                                                |  |  |  |  |  |  |

|                                          | 2<br>3                               | ]   |                                                          | Slot designation signal for addresses $4000(H) \sim 7FFF(H)$                                                                                                                                                                                                                |  |  |  |  |  |  |

|                                          | 4<br>5                               | W/R |                                                          | Slot designation signal for addresses $8000(H) \sim BFFF(H)$                                                                                                                                                                                                                |  |  |  |  |  |  |

|                                          | 6<br>7                               | ]   |                                                          | Slot designatior. signal for addresses C000(H)~FFFF(H)                                                                                                                                                                                                                      |  |  |  |  |  |  |

| Keyboard<br>return                       | 0<br>1<br>2<br>3<br>4<br>5<br>6<br>7 | R   | X0<br>X1<br>X2<br>X2<br>X3<br>X3<br>X3<br>X5<br>X5<br>X7 | Keyboard return signal                                                                                                                                                                                                                                                      |  |  |  |  |  |  |

| Registers for<br>keyboard<br>drive, etc. | 0<br>1<br>2<br>3                     |     | YA<br>YB<br>YC<br>YD                                     | $\left. \begin{array}{c} \\ \\ \\ \end{array} \right\} YA \sim YD \text{ signals for keyboard drive} \\ \\ \\ \end{array}$                                                                                                                                                  |  |  |  |  |  |  |

|                                          | 4                                    | W/R |                                                          | REM signal for cassette control                                                                                                                                                                                                                                             |  |  |  |  |  |  |

|                                          | 5                                    | ]   |                                                          | CMO signal for cassette write                                                                                                                                                                                                                                               |  |  |  |  |  |  |

|                                          | 6                                    | ]   |                                                          | CAPS signal for CAPS lamp (LED)                                                                                                                                                                                                                                             |  |  |  |  |  |  |

|                                          | 7                                    |     |                                                          | PPISND signal for sound                                                                                                                                                                                                                                                     |  |  |  |  |  |  |

| Mode<br>setting                          | 0<br>1<br>2<br>3<br>4<br>5<br>6<br>7 | w   | 0<br>1<br>0<br>0<br>0<br>0<br>0<br>1                     | The slot designation register and register for<br>keyboard drive and other functions are cleared when the level<br>shown on the left is given. This is the equivalent<br>function to setting the PA and PC ports to<br>output and PB port to input for MODE 0 of the 8255A. |  |  |  |  |  |  |

|                                          | 0                                    |     | Bo                                                       | Bits of the register for keyboard drive, etc., can<br>be set and reset when the level shown on the left is given. $B_1 \sim B_3$                                                                                                                                            |  |  |  |  |  |  |

|                                          | 1<br>2<br>3                          | w   | B1<br>B2<br>B3                                           | Bs express the bit numbers and the bits are set when Bo is "1",<br>and reset when "0".                                                                                                                                                                                      |  |  |  |  |  |  |

|                                          | 4<br>5<br>6<br>7                     |     | 0<br>0<br>0<br>0                                         |                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |

# Bit allocations of keyboard and slot designation registers

#### Back-up RAM (8 bit X 16)

After the ASCII ID number FE (H) is written to the I/O address 40 (H), the inverted value of 01 (H) can be obtained when I/O address 40 (H) is read, indicating that the back-up RAM (8 bit X 16) and bit map function can be used. If the RAM address (X0 (H) - XF (H)) is then set by the lower four bits of the address data of I/O address 40 (H), data can be written or read at I/O address 42 (H).

#### Bit map function

As was indicated in the above section on the back-up RAM (8 bit X 16), writing data two or more times in succession to I/O address 46 (H) after access of I/O address 40 (H), also writes data to I/O address 46 (H). When I/O address 47 (H) is then read, the last data written to I/O address 46 (H) is obtained when bit 7 of the data written to I/O address 47 (H) is "0". The data which was written second to last is obtained when bit 7 is "0". Then, the data written to I/O address 47 (H) is shifted up one bit so that data of bit 7 becomes bit 0. This allows for data to be obtained according to the level of bit 7 each time I/O address 47 (H) is read.

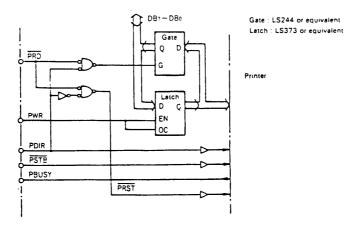

#### Printer

The following external circuit is necessary for bi-directional operation.

PBUSY: If a signal is input to the PBUSY pin and read, the same level as input to B1 is output.

| I/O address | R/W | <b>B</b> 7 | B6 | B5 | <b>B</b> 4 | <b>B</b> 3 | <b>B</b> 2 | <b>B</b> 1 | BO          |

|-------------|-----|------------|----|----|------------|------------|------------|------------|-------------|

| 90 (H)      | R   |            |    | >  | <          | $\leq$     | $\langle$  |            | $\boxtimes$ |

**PSTB:** When B0 is set to "0" are written to, the level at the **PSTB** pin goes to "0" at the point when the WR sinnal returns "1".

| I/O address | R/W | B7                | <b>B</b> 6 | B5 | B4 | B3 | B2     | B1 | BO |

|-------------|-----|-------------------|------------|----|----|----|--------|----|----|

| 90 (H)      | w   | $\langle \rangle$ |            | >  | >< | <  | $\leq$ |    |    |

PWR: If data is written when PDIR is "1" in the output state, a PWR signal having positive polarity according to the pulse width of the WR signal is output to the PWR pin. The data is latched and output to the external circuit when this signal returns to "0". The level at the PWR pin is held at "1" if the input state is selected while PDIR is "0". When the output state is returned to again, the PWR pin remains at this level. The level goes to "0" when access of 91 (H) is completed.

| I/O address | R/W | <b>B</b> 7 | B6 | <b>B</b> 5 | B4   | <b>B</b> 3 | <b>B</b> 2 | <b>B</b> 1 | B0 |

|-------------|-----|------------|----|------------|------|------------|------------|------------|----|

| 91 (H)      | w   |            |    |            | Data |            |            |            |    |

**PRD:** If data is written when PDIR is "0" in the input state, a PRD signal having negative polarity according to the pulse width of the RD signal is output to the PRDpin. This signal opens the gate of the external circuit allowing for data to be read.

| I/O address | R ′W | <b>B</b> 7 | B6 | B5 | B4   | <b>B</b> 3 | B2 | Bl | <b>B</b> 0 |

|-------------|------|------------|----|----|------|------------|----|----|------------|

| 91 (R)      | w    |            |    |    | Data |            |    |    |            |

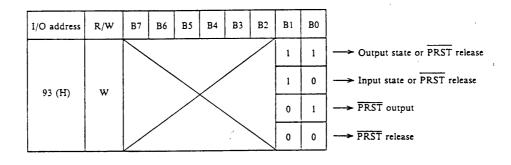

PDIR: If data is written with B1 = "1" and B0 = "1", a level of "1" is output continuously from the PDIR pin, and the MSX device is set to the output state. If data is written with B1 = "1" and B0 = "0" a level of "0" is output continuously from the PDIR pin, and the MSX device is set to the input state.

| I/O address | R/W | B7 | B6 | <b>B</b> 5 | B4 | <b>B</b> 3 | B2 | Bl | BO |                               |

|-------------|-----|----|----|------------|----|------------|----|----|----|-------------------------------|

|             |     |    |    |            |    | /          | /  | 1  | 1  | Output state or PRST release  |

| 93 (H)      | w   |    |    |            |    |            |    | 1  | 0  | > Input state or PRST release |

| ,           |     |    | /  |            |    |            |    | 0  | 1  | > PRST output                 |

|             |     |    |    |            |    |            |    | 0  | 0  | > PRST release                |

The PRST signal can be generated by the external circuit.

When the device is reset, and data is written with B1 = "0" and B0 = "1", the  $\overline{PRD}$  pin outputs "0" continuously and the PDIR pin outputs "1". The  $\overline{PRST}$  signal is created from these two signals.

The  $\overrightarrow{PRST}$  signal is released by writing data with the levels of the two bits set to another combination than B1 = "0" and B0 = "1".

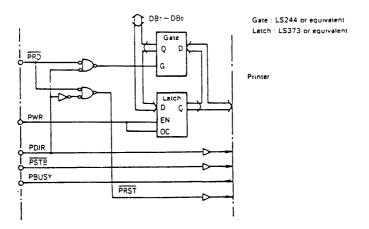

## Printer

The following external circuit is necessary for bi-directional operation.

PBUSY: If a signal is input to the PBUSY pin and read, the same level as input to B1 is output.

| I/O address | R/W | <b>B</b> 7 | <b>B</b> 6 | B5 | B4 | <b>B</b> 3 | B2     | Bl | <b>B</b> 0  |

|-------------|-----|------------|------------|----|----|------------|--------|----|-------------|

| 90 (H)      | R   |            | $\geq$     | >  | <  | <          | $\leq$ |    | $\boxtimes$ |

**PSTB:** When B0 is set to "0" are written to, the level at the **PSTB** pin goes to "0" at the point when the WR sinnal returns "1".

| I/O address | R/W | <b>B</b> 7 | <b>B</b> 6 | B5     | B4 | <b>B</b> 3 | B2     | B1 | B0 |

|-------------|-----|------------|------------|--------|----|------------|--------|----|----|

| 90 (H)      | w   |            | $\geq$     | $\geq$ | ~  | $\leq$     | $\leq$ |    |    |

PWR: If data is written when PDIR is "1" in the output state, a PWR signal having positive polarity according to the pulse width of the WR signal is output to the PWR pin. The data is latched and output to the external circuit when this signal returns to "0". The level at the PWR pin is held at "1" if the input state is selected while PDIR is "0". When the output state is returned to again, the PWR pin remains at this level. The level goes to "0" when access of 91 (H) is completed.

| I/O address | R/W | <b>B</b> 7 | B6 | <b>B</b> 5 | B4   | <b>B</b> 3 | <b>B</b> 2 | <b>B</b> 1 | <b>B</b> 0 |

|-------------|-----|------------|----|------------|------|------------|------------|------------|------------|

| 91 (H)      | w   |            |    |            | Data |            |            |            |            |

**PRD:** If data is written when PDIR is "0" in the input state, a  $\overline{PRD}$  signal having negative polarity according to the pulse width of the  $\overline{RD}$  signal is output to the  $\overline{PRD}$  pin. This signal opens the gate of the external circuit allowing for data to be read.

| I/O address | R /W | <b>B</b> 7 | B6 | B5 | B4   | <b>B</b> 3 | B2 | Bl | <b>B</b> 0 |

|-------------|------|------------|----|----|------|------------|----|----|------------|

| 91 (R)      | w    |            |    |    | Data |            |    |    |            |

PDIR: If data is written with B1 = "1" and B0 = "1", a level of "1" is output continuously from the PDIR pin, and the MSX device is set to the output state. If data is written with B1 = "1" and B0 = "0" a level of "0" is output continuously from the PDIR pin, and the MSX device is set to the input state.

The PRST signal can be generated by the external circuit.

When the device is reset, and data is written with B1 = "0" and B0 = "1", the PRD pin outputs "0" continuously and the PDIR pin outputs "1". The PRST signal is created from these two signals.

The  $\overrightarrow{PRST}$  signal is released by writing data with the levels of the two bits set to another combination than B1 = "0" and B0 = "1".

## Kanji ROM select signal and system control

I/O addresses D8 and D9 (H) are kanji ROM selection signal outputs. The level of these outputs is controlled by the system control indicated below.

Output to the KANJI pin is enabled when data is written when B0 of the system control data is "1".

| I/O address | R/W | B7 | B6     | B5     | B4 | <b>B</b> 3 | B2     | <b>B</b> 1 | B0 |

|-------------|-----|----|--------|--------|----|------------|--------|------------|----|

| F5 (H)      | w   |    | $\geq$ | $\geq$ | ~  | $\leq$     | $\leq$ |            |    |

#### Mapper

Mapper address

.

There are four mapper registers  $(0 \sim 3)$  located at I/O addresses FC (H) through FF (H). The effective bits is five for each, B4~B0, and these correspond to mapper addresses MA18~14. Mapper register pages  $0 \sim 3$  are selected according to addresses AB15 and AB14, and the contents are output as an address.

Thus, for example, if mapper addresses MA18~14 are used for 512K byte of RAM, the 512K byte indicated by the mapper register is divided into 32 sections. Each of these 16K byte areas can be selectively accessed by AB15 and AB14, making the addresses seem to increase.

| I/O address | R/W | B7               | B6       | B5            | B4 | В3 | B2 | Bl | B0 | Register               | AB15 | AB14 |

|-------------|-----|------------------|----------|---------------|----|----|----|----|----|------------------------|------|------|

| FC (H)      | R/W | $\triangleright$ | $\sim$   | <             |    |    |    |    |    | Mapper register page 0 | 0    | 0    |

| FD          | R/W | $\triangleright$ | $\sim$   | $\geq$        |    |    |    |    |    | Mapper register page 1 | 0    | 1    |

| FE          | R/W | $\triangleright$ | $\times$ |               |    |    |    |    |    | Mapper register page 2 | 1    | 0    |

| FF          | R/W | $\square$        | $\sim$   | $\overline{}$ |    |    |    |    |    | Mapper register page 3 | 1    | 1    |

MA18 MA17 MA16 MA15 MA14

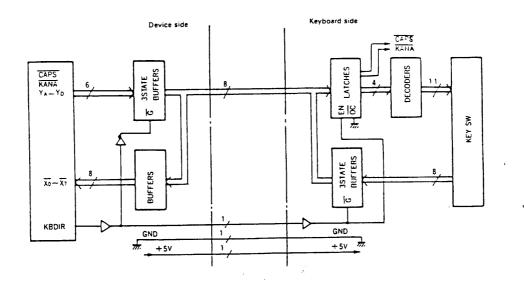

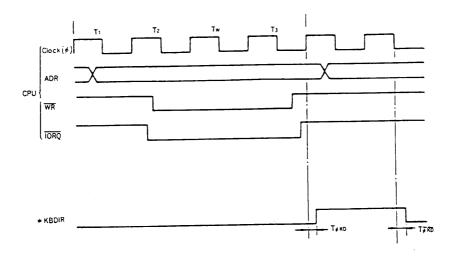

## Keyboard bus direction

This signal outputs 1 1/2 bits at the end of the I/O cycle when data is written to I/O address AA (H) or AB (H). Use of a circuit similar to that shown below allows for the number of signal lines between the keyboard and main system to be reduced.

## Keyboard bus direction

This signal outputs 1 1/2 bits at the end of the I/O cycle when data is written to I/O address AA (H) or AB (H). Use of a circuit similar to that shown below allows for the number of signal lines between the keyboard and main system to be reduced.

# 4. SSG and general purpose ports

The SSG (Software-controlled Sound Generator) is controlled by 14 registers (these registers can be read with no effect on sound).

Sound generation uses three square wave generator capable of voicing over 8 octaves, a pseudo-random noise generator, 5 bit envelope generator for single shot and repetitious attenuation, volume controller, mixer for combining music (tones) and noise, and a 5 bit D-A convertor. The general purpose port section consists of an input and output port which can be accessed through R/W registers.

#### Register array

When the upper bits, DB7~DB0, of the 8 bit address data is 0(H), the lower four bits, DB3~DB0, select the 15 registers. Address data which is fetched is held until the next address is fetched, and is not affected by read or write operations.

The contents of the register array is shown below.

#### Register array

| Regis-<br>ter | Address<br>(H) | Function Bit                            | <b>B</b> 7       | B6       | Bs       | В        | B3       | B2       | Bı      | Bo     |  |

|---------------|----------------|-----------------------------------------|------------------|----------|----------|----------|----------|----------|---------|--------|--|

| Ro            | 00             |                                         |                  |          | 8 bit fi | ne tone  | adjust   | ment     |         |        |  |

| Rı            | 01             | Frequency of channel A                  | $\geq$           | >        | $\sim$   |          | 4 bit re | ough to  | ne adju | stment |  |

| R2            | 02             |                                         |                  |          | 8 bit fi | ne tone  | adjust   | ment     |         |        |  |

| RJ            | 03             | Frequency of channel B                  |                  | >        | <        | $\leq$   | 4 bit r  | ough 10  | ne adju | stment |  |

| R4            | 04             |                                         |                  |          | 8 bit fi | ne tone  | adjust   | ment     |         |        |  |

| Rs            | 05             | Frequency of channel C                  |                  | >        | <        |          | 4 bit r  | ough 10  | ne adju | sument |  |

| R6            | 06             | Frequency of noise                      |                  | $\sim$   | <        | 5 bit    | noise fr | equebo   | y       |        |  |

| <u> </u>      | 1              |                                         |                  | rt *     | 1        | Noise    |          | Tone     |         |        |  |

| R7            | 07             | General purpose port and mixer settings | "1"              | -0-      | с        | в        | A        | с        | В       | A      |  |

| Rs            | 08             | Level of channel A                      | $\square$        | >        | <        | м        | L3       | 12       | LI      | Lo     |  |

| Ro            | 60             | Level of channel B                      | $\square$        | >        | <        | м        | L3       |          | Lı      | 10     |  |

| RA            | 0A             | Level of channel C                      | $\triangleright$ | $\geq$   | <        | М        | L        | 12       | Lı      | Lo     |  |

| RB            | OB             | 1                                       |                  |          | 8 bit f  | ine adji | usumen   | 1        |         |        |  |

| RC            | 0C             | Frequency of envelope                   |                  |          | 8 bit 1  | ough a   | djustm   | ent      |         |        |  |

| RD            | 0D             | Shape of envelope                       |                  | $\geq$   | $\sim$   | $\leq$   | CONT     | ATT      | ALT     | HOLD   |  |

| $\square$     | 0E             | Data of general purpose input port      |                  |          |          | •        |          | hit alla | -       | mhle - |  |

| RF            | 0F             | Data of general purpose output port     |                  | fer to g | reneral  | ршроз    | e port   |          |         |        |  |

\* Make sure that the section of R7 for ports is at the indicated levels.

#### General purpose ports

The input port is at address 0E(H) and the output port at address 0F(H). These ports are controlled by the register for output port data hold register RF. The general purpose port bit allocation table on the right shows the relationship between each of the bits, and the input/output pins.

| Port   | Bit                                          | Input | Names of connected pins                                                                                                  |

|--------|----------------------------------------------|-------|--------------------------------------------------------------------------------------------------------------------------|

| Input  | Bo<br>B1<br>B2<br>B3<br>B4<br>B5<br>B6<br>B7 | i     | FW1 or FW2BACK1 or BACK2LAFT1 or LAFT2RIGHT or RIGHT2TRGA1 or TRGA2JIS/50CM1                                             |

| Output | B0<br>B1<br>B2<br>B3<br>B4<br>B5<br>B6<br>B7 | o     | TRGA1<br>TRGB1<br>TRGA2<br>TRGB2<br>STB1<br>STB2<br>Input selection for input port B0~B5 (not externally output)<br>KANA |

General purpose port bit allocation table

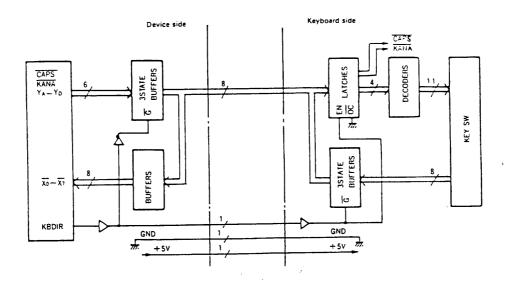

## Setting of music frequencies (controlled by registers $R_0 \sim R_3$ )

The frequencies of the square wave generated by the music generators for the three channels (A, B, and C) are set by registers  $R_0$  through  $R_3 R_0$  and  $R_1$  control channel A,  $R_2$  and  $R_3$  are used for channel B, and  $R_4$  and  $R_5$  control channel C. The oscillation frequency  $F_T$  is obtained in the following manner from value of the register TP (decimal). Fø is the clock frequency.

$$F_T = \frac{Fø}{32TP}$$

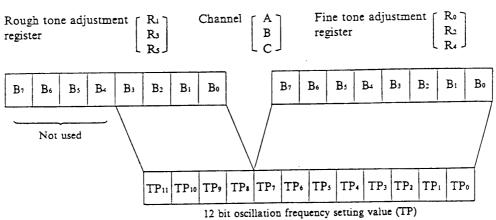

## Setting of noise generator (controlled by register R<sub>6</sub>)

The noise frequency FN is obtained from the register value NP (decimal) in the following manner. Fø is the clock frequency.

$$F_N = \frac{F\sigma}{32NP}$$

Noise frequency register R6

5 bit noise frequency setting value (NP)

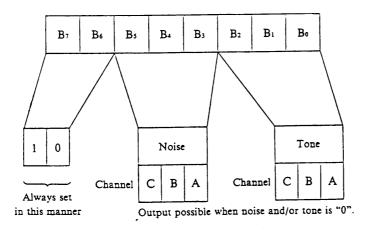

#### Settings of mixer (controlled by register R<sub>1</sub>)

The mixer is used to combine music and noise components. The combination is determined by bits  $B_5 \sim B_0$  of register  $R_7$  Sound is output when a "0" is written to the register. Thus, when both the noise and tone are "0", the output is combined by the mixer. Whichever is "0" is output, and nothing is output when both are "1".

Mixer setting register R7

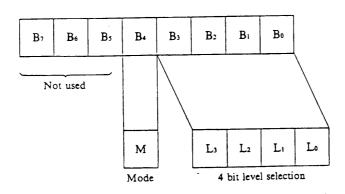

## Level control (controlled by registers $R_* \sim R_A$ )

The audio level output from the D/A convertors for the three channels (A. B, and C) is adjusted by registers Rs, Rs, and RA). Mode M selects whether the level is fixed (when M = 0) or variable (M = 1). When M = 0, the level is determined from one of 16 by level selection signals L3, L2, L1, and L0 which compromise the lower four bits. When M = 1, the level is determined by the 5 bit output of E4, E3, E2, E1, and E0 of the built-in envelope generator. This level is variable as E4 ~ E0 change over time.

Level setting registers  $\begin{bmatrix}

R_8 : Channel A \\

R_9 : Channel B \\

R_A : Channel C

\end{bmatrix}$

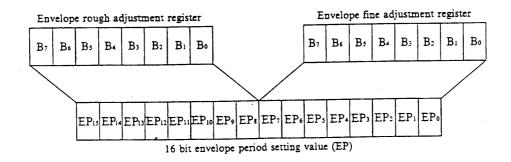

## Setting of envelope frequency (controlled by registers $R_B$ and $R_c$ )

The envelope repetition frequency  $F_E$  is obtained as follows from the envelope frequency setting value  $E_P$  (decimal). Fø is the clock frequency.

$$F_{E} = \frac{F\emptyset}{512 EP}$$

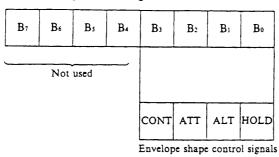

## Envelope shape control (controlled by register R<sub>D</sub>)

The envelope level is determined by the envelope generator using the 5 bits  $L_4 \sim L_0$ . The shape of this envelope is created by increasing, decreasing, stopping, or repeating the counter for the envelope generator. The shape is controlled by bits  $B_3 \sim B_0$  of the register  $R_D$ .

Envelope shape control register RD

The envelope can take the shapes shown in the table below according to combinations of the CONT, ATT, ALT, and HOLD signals.

| B3   | B2  | Bı  | Bo   | Familian share                         |

|------|-----|-----|------|----------------------------------------|

| CONT | ATT | ALT | HOLD | Envelope shape                         |

| 0    | 0   | x   | x    |                                        |

| 0    | 1   | x   | x    |                                        |

| 1    | 0   | 0   | 0    |                                        |

| 1    | 0   | 0   | 1    |                                        |

| 1    | 0   | 1   | 0    |                                        |

| 1    | 0   | 1   | 1    |                                        |

| 1    | 1   | 0   | 0    |                                        |

| 1    | 1   | 0   | 1    |                                        |

| 1    | 1   | 1   | 0    |                                        |

| 1    | 1   | 1   | 1    |                                        |

|      |     |     | →    | 1/fe   - Repetition period of envelope |

Table of envelope shapes

#### **D-A** Convertor

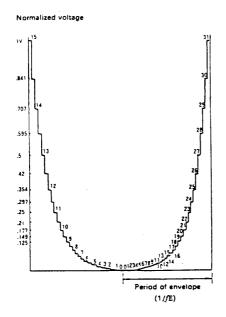

When the D-A convertor normalizes the maximum amplitude to 1V, the output changes as shown in the diagrams below. This conversion from linear input to logarithmic output provides a wide dynamic range and a natural feeling of attenuation.

Fig. 1 Output level of DA convertor The subscripts on the left half of the diagram are the fixed levels of the selection signals L<sub>3</sub>, L<sub>2</sub>, L<sub>1</sub>, and L<sub>0</sub> converted into decimal values. The subscripts on the right side are decimal expressions of the envelope counter output signals E<sub>4</sub>, E<sub>3</sub>, E<sub>2</sub>, E<sub>1</sub>, and E<sub>0</sub>.

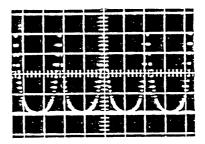

Fig. 2 Output waveform of single tone with envelope (RD = XXXX1110)

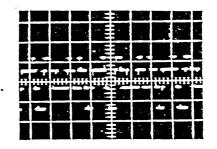

Fig. 3 Output waveform from mixing of three sounds with fixed level  $(R_D \sim R_A = XXXX1100)$

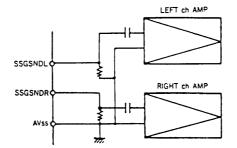

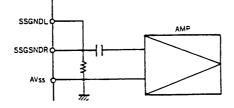

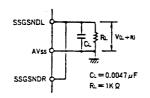

## Sound output SSGSNDL and SSGSNDR

Of the music signals generated on channels A, B, and C by the data set in the registers, channel B is output from the SSGSNDL pin and channel C is output from the SSGSNDR pin. Channel A is the mixed signal from the SSGSNDL and SSGSNDR pins. Output is thus stereo output having left and right output signals. Monaural output is also possible by shorting the the SSGSNDL and SSGSNDR pins when not in use.

Possible configuration for stereo output

Possible configuration for monaural output

.

## 5. Clock and RAM (4 bit $\times$ 26)

The clock section is connected to the crystal oscillation circuit and provides second, minute, hour, day of the week, day, month, and year clock counter functions, and minute, hour, day of the week, and day alarm registers. Control such as setting and reading the clock data for time and calender and alarm data is carried out in this section. All of this data can be backed up.

## Address allocations and initial state of counters and registers

Regardless of the value of the upper four bits of the 8 bit address data, the mode is selected from the low four bits  $DB_3 \sim DB_0$  and the four modes indicated by the address X D (H) modes registers M1 and M0. Addresses X 0 (H) ~ X C (H) can be are both writable and readable. Address X D (H) ~ X F (H) is write only, and has no effect on the mode.

The state of the counters and registers is indeterminate when the power is turned on. They must be set by writing the prescribed values.

| Mode          |                         |                  |    |    |    |                                   | 1                |              |        |        | 2        | 3        |

|---------------|-------------------------|------------------|----|----|----|-----------------------------------|------------------|--------------|--------|--------|----------|----------|

| Adress<br>(H) | Function Bit            | Вз               | B2 | Bı | Bo | Function Bit                      | <b>B</b> 3       | <b>B</b> 2   | Bı     | Bo     | Function | Function |

| × 0           | 1 second counter        |                  |    |    |    | $\geq$                            |                  | $\geq$       | $\leq$ | $\leq$ | ļ        | ł        |

| × 1           | 10 second counter       | $\boxtimes$      |    |    |    | $\geq$                            |                  | $\geq$       | $\leq$ | $\leq$ |          |          |

| x 2           | 1 minute counter        |                  |    |    |    | 1 minute alarm register           |                  | <del>.</del> |        |        | RAM      | RAM      |

| x 3           | 10 minute counter       | $\boxtimes$      |    |    |    | 10 minute alarm register          | $\geq$           |              |        |        | 4 Bit    | 4 Bit    |

| x 4           | 1 hour counter          |                  |    |    |    | 1 hour alarm register             |                  |              |        |        | ×<br>13  | 13       |

| x 5           | 10 hour counter         | $\triangleright$ | <  |    |    | 10 hour alarm register            | $\triangleright$ | $\leq$       |        |        |          |          |

| x 6           | Day of the week counter | $\mathbb{X}$     | ]  |    |    | Day of the week alarm<br>register | $\mathbb{X}$     | ]            |        |        |          |          |

| × 7           | 1 day counter           |                  |    |    |    | l day alarm register              |                  |              |        |        | 1        |          |

| × 8           | 10 day counter          | $\triangleright$ | <  |    |    | 10 day alarm register             | $\triangleright$ | $\leq$       |        |        |          |          |

| x 9           | 1 month counter         |                  |    |    |    |                                   |                  |              |        | >      | 1        |          |

| x A           | 10 month counter        | $\triangleright$ | >  | <  |    | 12/24 hour selector               |                  | $\geq$       | $\leq$ |        | , ·      |          |

| x B           | 1 year counter          |                  |    |    |    | Leap year calender                | $\triangleright$ | $\leq$       |        |        |          |          |

| ×c            | 10 year counter         |                  |    |    |    | $\supset$                         | $\square$        | $\geq$       | $\leq$ | $\leq$ |          |          |

## Allocation of addresses and functions

| Address<br>(H) | Function                            | Bit | Вз        | B2         | Bı         | Bo    |  |  |

|----------------|-------------------------------------|-----|-----------|------------|------------|-------|--|--|

|                | Mode                                |     | Timer     | Alarm      | M          | ode   |  |  |

| ×D             | register                            |     | EN        | EN         | Mı         | M٥    |  |  |

|                | Test                                |     | Test      |            |            |       |  |  |

| хE             | register                            |     | T3        | T2         | <b>T</b> 1 | To    |  |  |

| ×F             | Reset controller<br>16/1Hz register |     | 1HZ<br>ON | 16HZ<br>ON |            | Alarm |  |  |

Note: The day of the week counter counts between 0 and 7. The relationship between actual day of the week and counter value can be determined as desired. .

# Mode setting and alarm/timer EN function (address x D (H))

The 4 bit mode register consists of  $M_1$  and  $M_0$  for switching the mode functions and two bits for the timer EN and alarm EN.

| Mode | Mi | Mo | Description                                               |

|------|----|----|-----------------------------------------------------------|

| 0    | 0  | 0  | Time and calender can be set and read                     |

| 1    | 0  | 1  | Alarm, 12/24 selection, and leap year can be set and read |

| 2    | 1  | 0  | RAM (4 bit x13) is both readable and writable             |

| 3    | 1  | 1  | RAM (4 bit x 13) is both readable and writable            |

| Function | Level | Description                            |  |

|----------|-------|----------------------------------------|--|

| Alarm    | 0     | Alarm signal not output to AML pin     |  |

| EN       | 1     | Alarm signal output to AML pin         |  |

| Timer    | 0     | Counter stopped for other than seconds |  |

| EN       | 1     | Clock started                          |  |

# Reset control function and 16Hz/1Hz register setting (address x F (H))

Alarm reset and timer reset function during the data write, and not have registers. There are registers for 16Hz ON and 1Hz ON. These function in the following manner.

| Function    | Level | Description                               |

|-------------|-------|-------------------------------------------|

| Alarm RESET | 1     | All alarm registers reset upon write.     |

| Timer RESET | 1     | Counter is reset from seconds upon write. |

| 16Hz ON     | 0     | 16Hz signal output to ALM pin.            |

| 1Hz ON      | 0     | 1Hz signal output to ALM pin.             |

## Test registers (addresses x E (H))

$T_3 \sim T_0$  are registers for test purposes. Tests are performed for all except test 0 (operation as clock). When using the clock for the first time, set all bits to level "0" in order to perform test 0 (clock).

| Test | <b>T</b> 3 | T2 | T۱ | T0 | Description                         |

|------|------------|----|----|----|-------------------------------------|

| 0    | 0          | 0  | 0  | 0  | Operation as clock.                 |

| 1    | 0          | 0  | 0  | 1  | Test 1 selected.                    |

| 2    | 0          | 0  | 1  | 0  | Test 2 selected                     |

| 3    | 0          | 0  | 1  | 1  | Test 3 selected. Output to ALM pin. |

| 4    | 0          | 1  | 0  | 0  | Test 4 selected.                    |

| 8    | 1          | 0  | 0  | 0  | Test 8 selected.                    |

#### Setting of 12/24 selector (mode 1, address x A (H) )

Selection of operation as a 12 hour clock or 24 hour clock is possible by writing the level shown in the table below. Set the time after making this setting.

| Function               | Level | Description                                                                                                                                                                        |

|------------------------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 12/24 hour<br>selector | 0     | Operation as 12 hour clock. When this mode is selected, the<br>10 hour counter and B1 of the alarm register indicated AM or PM.<br>AM is selected when B1 is "0", and PM when "1". |

|                        | 1     | Operation as 24 hour clock.                                                                                                                                                        |

#### Setting of leap year (mode 1, address x B (H) )

The leap year setting can be made by setting the levels shown in the table below. The time and calender settings are made after this setting is made. This calender is incremented together with the year calender.

| Function  | Bi | Bo | Description                                    |

|-----------|----|----|------------------------------------------------|

|           | 0  | 0  | Operation with this year as leap calender year |

| Leap year | 0  | 1  | Three years from now                           |

| counter   | 1  | 0  | Year after next as leap year                   |

|           | 1  | 1  | Next year as leap year                         |

## Setting and reading the time and calender (mode 0, address x 0 (H) $\sim$ x C(H) )

The addresses can be fixed by the functions indicated in the table for address allocations and functions. The clock counter can be set by writing effective values for time and calender clock data. Data is read in the same manner. The address is fixed and the bits are read to obtain the clock data. The level of bits which are not effective is always "0".

If the time of the second, minute, hour, day of the week, day or year counter (clock counter) advances while setting or reading the clock data, it is not possible to set or read the proper values for the clock data.

Thus when setting the clock data, generate a timer reset and set all necessary clock data during this second. An alternate procedure is to generate a clock EN to stop incremention of all counters except seconds, generate a timer reset, set all necessary clock data within one second, and then update the clock with the timer EN. When reading the clock data, read it twice and compare the results to determine usable data. Another approach is to set the clock timer to the operational state again with the timer EN and read the data. The change in the 1 second signal which occurs while the counter is stopped for all counting above one second, will be adjusted when clock is restarted. Approximately 100&mu.s are required for this correction. Be sure not read the time again during this period.

## Alarm setting and reading (mode 1, address x 2 (H) $\sim$ x 8 (H) )

The alarm registers can be set by fixing the addresses by the functions indicated in the table for address allocations and functions, and then by writing valid values to the bits for time and calender alarms. The data in the alarm registers can be obtained in the same manner by fixing the addresses, and reading the bits.

When the contents of the minute, hour, day of the week, day and year alarm registers is the same as the contents of the clock calender (and alarm EN register is set to output state), a level "0" signal is output to the  $\overline{\text{ALM}}$  pin.

The alarm register is reset by the alarm RESET bit. Then, the data written to the alarm register and clock counter are made the same. Regarding alarm registers which were not written to, output is to the ALM pin as the data of both were already the same.

ALM pin output (external load resistance is needed as open drain)

The signals controlled by the alarm En, 16HZON, 1HZON, and test registers can be output simultaneously from this pin. Set the level of the various registers so that only the required signals are output.

## RAM (4 bit x 26) (mode 2 and 3, address x 0 (H) ~ x C (H) )

This RAM area consists of a RAM area accessed at address X0 (H) ~ X C (H) in mode 2, and a RAM area accessed at address X 0 (H) ~ X C (H) in mode 3.

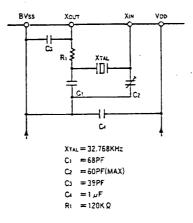

## 6. Oscillation circuit

A sample oscillation circuit is shown on the right.

Note that the accuracy of the clock will suffer if the oscillation circuit is effected by external noise. The voltage characteristics and temperature characteristics of the clock oscillation circuit, back-up voltage and current characteristics and back-up current and C3 characteristics are shown below. All parts other than the device itself are kept at room temperature during measurement of temperature characteristics.

## 9. Electrical characteristics

## Absolute maximum ratings

| ltem                                | Rated value           | Units |

|-------------------------------------|-----------------------|-------|

| Power supply voltage (VDD)          | $-0.3 \sim 7.0$       | v     |

| Input pin voltage                   | $-0.3 \sim VDD + 0.3$ | v     |

| Operational surrounding temperature | 0 ~ 70                | °C    |

# 10. Recommended operating conditions

| ltem                   | Symbol | Minimum | Typical | Maximum | Units |  |

|------------------------|--------|---------|---------|---------|-------|--|

| Power supply voltage   | VDD    | 4.75    | 5.00    | 5.25    | v     |  |

| Data retention voltage | VDE    | 2.0     |         | 5.25    | v     |  |

| Frequency for clock    | Fx     |         | 32.768  |         | Кнz   |  |

## 11. DC characteristics

| ltem                             | Symbol | Conditions                                             | Minimum     | Typical | Maximum | Units |

|----------------------------------|--------|--------------------------------------------------------|-------------|---------|---------|-------|

| Low level input voltage 1        | VILI   | Other than $(\overline{X}_0 \sim \overline{X}_1, XIN)$ | - 0.3       |         | 0.8     | V     |

| High level input voltage 1       | VIHI   | Other than $(\overline{X}_0 \sim \overline{X}_7, XIN)$ | 2.0         |         | VDD     | v     |

| Low level input voltage 2        | VIL2   | $(\overline{X}_0 \sim \overline{X}_1, XIN)$            | -0.3        |         | 1.5     | v     |

| High level input voltage 2       | VIH2   | $(\overline{X}_0 \sim \overline{X}_7, X]N)$            | 3. <b>5</b> |         | Vdd     | v     |

| Low level output voltage 1       | Vol    | IoL = Note 0)                                          | 0           |         | 0.5     | v     |

| High level output voltage 1      | Vон    | lol = Note 0)                                          | 4.0         |         | Vdd     | v     |

| Input current                    | Ъ      | $V_{IN} = 0^{V}$                                       | 50          |         | 500     | μА    |

| Input leak current               | Гц     | $V_{IN} = 0 \sim 5^{V}$                                |             |         | ±10     | μA    |

| Output leak current              | ILO    | $V_{IN} = 0 \sim 5^V$                                  |             |         | ±10     | μA    |

| Power supply voltage (hold)      | ldb    | $V_{DB} = 2.0^{V}$                                     |             |         | 15      | μA    |

| Power supply voltage (operating) | LDD    | $V_{DB} = 5.25^{V}$                                    | 1           |         | 35      | μA    |

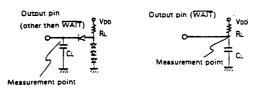

Note 0)  $I_{OL} = 10mA$  :Applies to  $\overline{WAIT}$ ,  $\overline{CAPS}$ , and  $\overline{KANA}$  pins  $I_{OL} = 2.4mA$  :Applies to output pins other than  $\overline{WAIT}$ ,  $\overline{CAPS}$ , and  $\overline{KANA}$ .  $I_{OH} = 0.2mA$  :Applies to all output pins other than open drain.

## 12. AC characteristics Note 1)

## Clock timing

| ltem               | Symbol | Conditions | Minimum | Typical | Maximum | Units |

|--------------------|--------|------------|---------|---------|---------|-------|

| Clock period       | Тс     |            |         | 280     |         | ns    |

| Rise time of clock |        |            |         |         | 30      | ns    |

| Fall time of clock | Tør    |            |         |         | 30      | ns    |

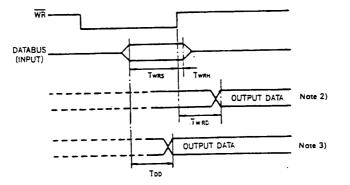

#### Write timing

| ltem                                               | Symbol | Conditions         | Minimum | Typical | Maximum | Units |

|----------------------------------------------------|--------|--------------------|---------|---------|---------|-------|

| Assurred time prior to data WR off                 | Twrs   |                    |         | 300     |         | ns    |

| Hold time from data $\overline{WR}$ off            | Twrh   |                    |         | 0       |         | ns    |

| Delay time from $\overline{WR}$ off of output data | Twrd   | Note 2) CL = 100PF |         |         | 250     | nş    |

| Delay time from output data                        | TDD    | Note 3) CL = 100PF |         |         | 250     | ns    |

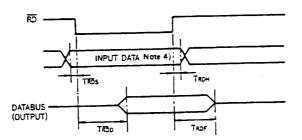

#### Read timing

| ltem                                              | Symbol       | Conditions | Minimum | Typical | Maximum    | Units    |

|---------------------------------------------------|--------------|------------|---------|---------|------------|----------|

| Data delay time<br>Transition time to float state | TRDD<br>TRDF |            |         |         | 250<br>100 | ns<br>ns |

| Assured time prior to input data RD               | TRDS         | Note 4)    |         | 0       |            | ns<br>ns |

| Hold time for input data RD                       | Trdh         | ٠<br>١     |         | 0       |            | 113      |

- Note 1) The various timing characteristics assume that direct connection is made to the address bus, data bus, and control bus signals of the CPU.

- Note 2) Applies to YA, YB, YC, YD, REM, CMO, CAPS, and PPISND pins.

- Note 3) Applies when TRGA1, TRGB1, STB1, STB2, TRGA2, TRGB2, KANA, PDIR, PWR, and PRD pins are controlled by data bus.

- Note 4) Applies to X0, X1, X2, X3, X4, X5, X6, X7, FWD1, BACK1, LEFT1, RIGHT1, TRGA1, TRGB1, FWD2, BACK2, LEFT2, RIGHT2, TRGA2, TRGB2, CML and PBUSY pins.

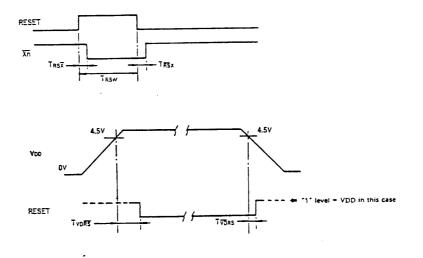

#### **Reset timing**

| ltem                                                  | Symbol | Conditions                                                                          | Minimum | Typical | Maximum | Units |

|-------------------------------------------------------|--------|-------------------------------------------------------------------------------------|---------|---------|---------|-------|

| RESET $\uparrow \overline{X_n} \downarrow$ delay time | Trsx   | $\overline{X_n} = (\overline{X_1}, \overline{X_2}, \overline{X_3}, \overline{X_5})$ |         |         | 150     | ns    |

| RESET ↓ Xn ↑ delay time                               | TRSX   | $\int \overline{X_6}, \overline{X_7}$                                               | 50      |         |         | ns    |

| RESET † RESET 1 time                                  | Trsw   |                                                                                     | 5.6     |         |         | μs    |

| VDD (4.5) ↑ RESET ↓ delay time                        | TVDRS  |                                                                                     | 5.6     |         |         | μs    |

| VDD (4.5) ↓ RESET † delay time                        | TVDRS  |                                                                                     |         |         | 0       | μs    |

#### Analog output

| Item                                     | Symbol | Conditions          | Minimum | Typical | Maximum | Units    |

|------------------------------------------|--------|---------------------|---------|---------|---------|----------|

| Output voltage from channel A to SSGSNDL | VAL    | )                   | 0.28    | 0.35    | 0.44    | Vpp      |

| Output voltage from channel A to SSGSNDR | Var    | Note 7) and Note 9) | 0.28    | 0.35    | 0.44    | $V_{pp}$ |

| Output voltage from channel B to SSGSNDL | VBL    |                     | 0.52    | 0.66    | 0.83    | Vpp      |

| Output voltage from channel C to SSGSNDR | Vcr    | J                   | 0.52    | 0.66    | 0.83    | Vpp      |

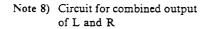

| Output voltage when SSGSNDR and SSGSNDL  | V(L+R) | Note 8) and Note 9) | 0.42    | 0.53    | 0.67    | Vpp      |

| are connected                            |        |                     |         |         |         |          |

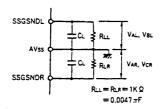

Note 7) Circuit for separate output of L and R

Note 9) State of registers during SSGSNDL and SSGSNDR output voltage measurement

Music frequency setting : 0FF (H) (~440Hz)

register

Volume control register : 0F (H) (max. volume) Mixer register : Separate output of A, B, and C channels

| I            | tem        | Symbol | Conditions                          | Mini-<br>mum | Maxi-<br>mum | Units |

|--------------|------------|--------|-------------------------------------|--------------|--------------|-------|

| MREQ + WAIT  | delay tim  | TMRWA  | CL = 100PF RL = 1 Kn                |              | 150          | ns    |

| Clok 1 WAIT  | •          | TØWA   | -                                   |              | 150          | ns    |

| MREO I RAS   | 1          | TMRRA  | $CL = 100PF R_{L} = 3.9 K_{\Omega}$ |              | 70           |       |

| MREQ T RAS   | -<br>1 -   | TMRRA  |                                     |              | 70           |       |

| Clok T RAS   | 1          | TØRA   | -                                   |              | 70           | -     |

| Clok 1 RAS   | ÷<br>† -   | TØRA   |                                     | 90           | 180          | -     |

| Clok 1 MPX   | † -        | ТØмх   | -                                   |              | 70           | -     |

| MREO † MPX   | 1 -        | TMRMX  | ~                                   |              | 70           | -     |

| RAS I MPX    | -<br>1 -   | TRAMX  |                                     | 50           |              | -     |

| Clok 1 CAS   | -          | TØGA   | -                                   |              | 70           | -     |

| MREQ T CAS   | -<br>1 -   | TMRCA  | -                                   |              | 70           | -     |

| Clok I CAS   | ,<br>† -   | ТОсл   | -                                   |              | 70           | -     |

| RD I WE      | ,<br>† -   | TØwe   | -                                   |              | 70           | -     |

| Clok I WE    | 1 -        | TOWE   | -                                   |              | 70           | -     |

| MREQ 1 *CSn  |            | TMRCS  | -                                   |              | 70           | -     |

| MREO † *CSn  | t -        | TMRCS  | -                                   |              | 70           | -     |

| MREO 1 *SLT  | •          | TMRSL  | -                                   | •            | 70           | -     |

| MREQ 1 *SLT  | •          | TMRSL  | -                                   |              | 70           | -     |

| MREO I *SLT  | nn 1 -     | TMRST  | -                                   |              | 70           | -     |

| MREQ 1 *SLT  |            | TMRST  | -                                   |              | 70           | -     |

| ADR *MA      | <u>n</u> - | TDMA   | -                                   |              | 120          | -     |

| ADR(OFF) *MA | n(OFF) -   | TADMA  | -                                   |              | 120          | -     |

|              |            | TROVR  | -                                   |              | 70           | -     |

| RD T VDPC    | TR† -      | TRDVR  | -                                   |              | 70           | -     |

| Clok 1 VDPC  | - IW       | TØVW   | -                                   |              | 70           | -     |

| WR T VDPC    | cw; -      | TWRVW  | -                                   |              | 40           | -     |

| IORQ 1 KAN   | Π1 -       | TIOKN  | -                                   |              | 70           | -     |

| IORQ 1 KAN   | Л † –      | TIOKN  | -                                   |              | 70           | -     |

| RD 1 PRD     | 1 -        | TROPR  | -                                   |              | 150          | -     |

| RD 1 PRD     | t -        | TRDPR  | -                                   |              | 150          | -     |

| WR 1 PWR     | t -        | TWRPW  | -                                   |              | 150          | -     |

| WR î PWR     | - 1        | TWRPW  | -                                   |              | 150          | -     |

| Clok † KBD   | IR† -      | TØKD   | -                                   |              | 150          | -     |

| Clok ! KBD   | IR 1 -     | TØRD   | -                                   |              | 150          | -     |

|              |            |        |                                     |              |              |       |

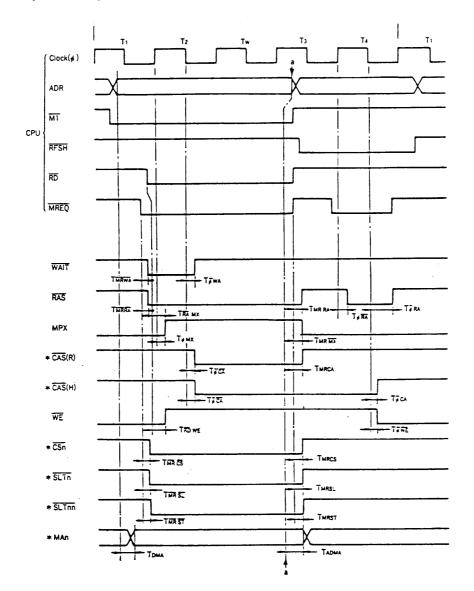

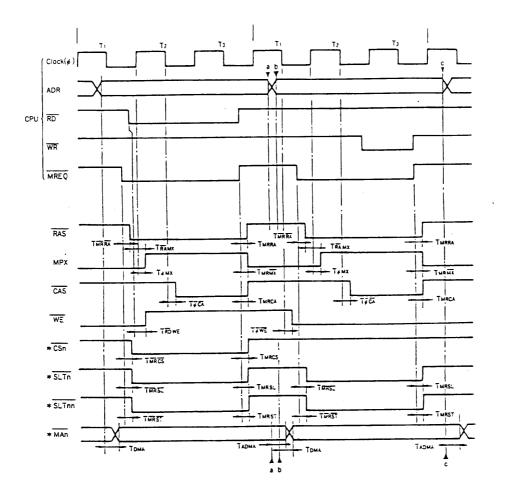

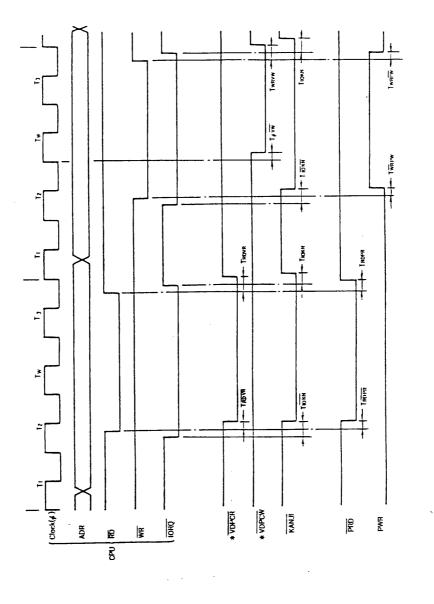

Timing of M1 cycle, Memory read/write cycle, and I/O cycle

Note 5: Refer to Note 10 for those marked with asterisks.

Note 6: The load circuit is shown on the right.

# Clock timing

| Clock(#) | "H"<br>$V_{DD} - 0.6^{v}$<br>$2.0^{v}$<br>$\Delta^{v}$ | "L"<br>0.8"<br>0.8"<br>0.8"<br>±0.5" |

|----------|--------------------------------------------------------|--------------------------------------|

|----------|--------------------------------------------------------|--------------------------------------|

# Write timing

## Read timing

## M1 cycle timing

Note 10: Refer to the following for signals marked with asterisks

$\overline{CAS}(R):\overline{CAS}$  signal in RAS only refresh mode

CAS (H) : CAS signal in hidden refresh mode

CAn : CS1, CS2, CS12, and CS0 and CS01 of SLT02/CS0 and ;us onSLT03/CS01

SLTn : SLT1 and SLT2 output

- SLTnn : SLT3/30, SLT31, SLT32, STL33, SLT0/00, SLT01, SLT02/CS0, SLT02 of SLT03/CS01, and  $\overline{SLT03}$  output

- MAn : MA14, MA15, MA16, MA17, and MA18 output of MA18/KBDIR

# Memory read/write cycle timing

Note 11: Refer to Note 10 for signals marked with asterisk

Note 12: The VDPCR and VDPCW signals marked with asterisks indicate the timing when "1" is applied to the X7 pin during reset. A 1 bit wait is inserted after Tw when "0" is applied to the X7 pin during reset.

## I/O cycle timing (2)

Note 13: The signal marked with an asterisk is the KBDIR output of MA18 when "1" is applied to the  $\overline{X5}$  during reset.

## Reset timing

# 14. External view